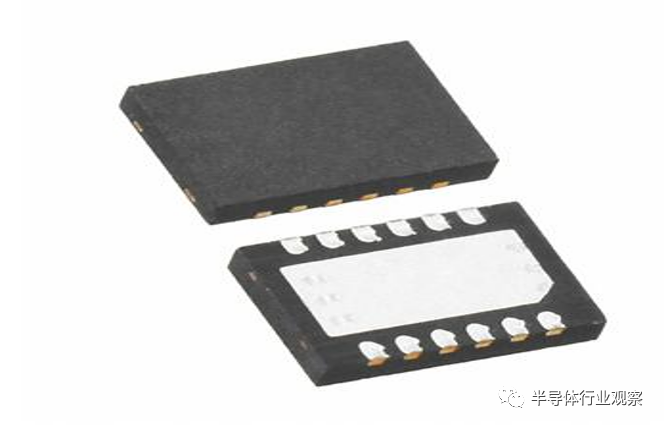

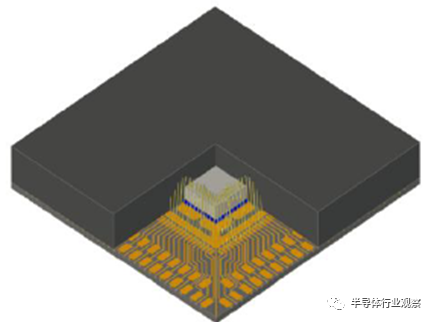

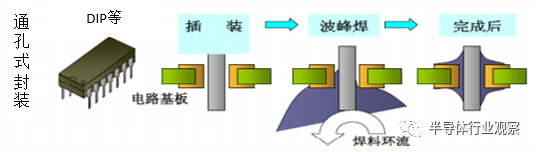

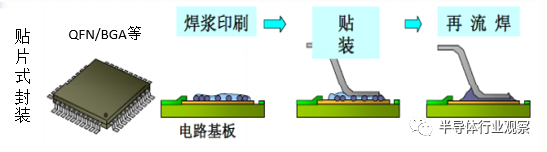

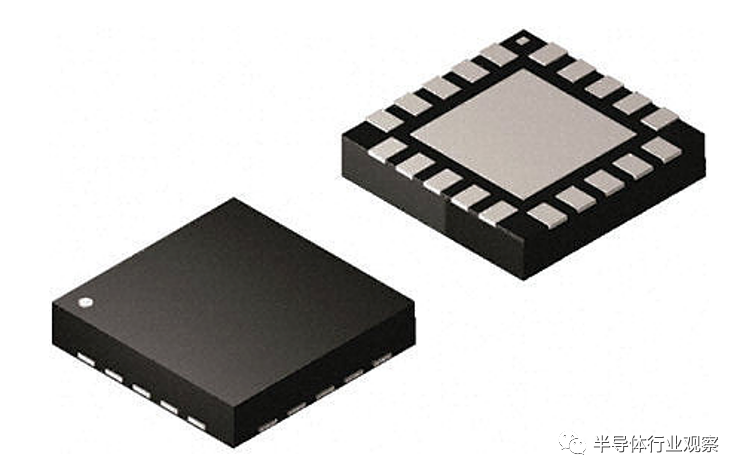

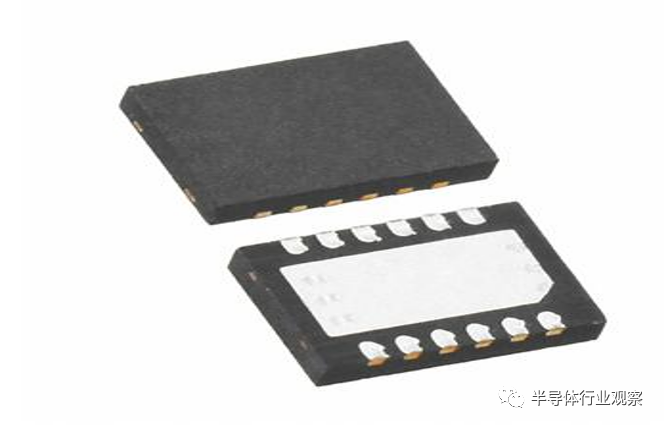

通常而言芯片产业链可分为三个大的领域:电路设计、晶圆制造和芯片封装测试,芯片封装测试属于产业链中的后端流程。按照电子产品终端厂对封装好芯片的组装上板方式,芯片封装形式可以分为通孔式封装(图-1)和贴片式封装(图-2)。而其中贴片式封装类型中有一种封装形式特别受市场欢迎,那就是QFN封装(图-3)。QFN是日本电子机械工业协会定义的名称,取英文Quad Flat No-lead Package的首字母简写,中文全称叫方形扁平无引脚封装;DFN(Dual Flat No-lead Package)封装属于QFN封装的延伸封装。DFN封装(图-4)的管脚分布在封装体两边且整体外观为矩形,而QFN封装的管脚分布在封装体四边且整体外观为方形。

图3

图4

图4

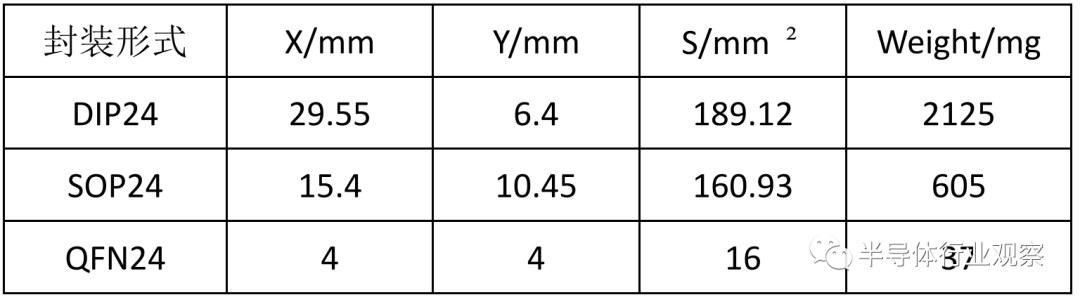

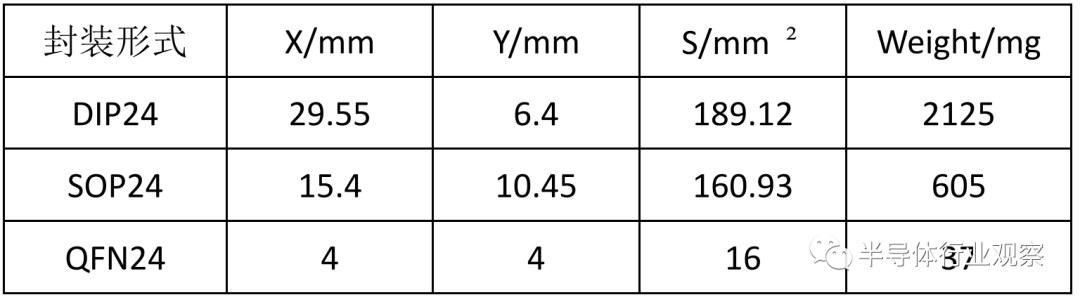

为什么QFN封装会在芯片市场上受欢迎、被众多芯片设计公司选用呢?我们可以从下面三个角度进行简单说明:物理方面、品质方面、性价比。现在的电子产品有个明显趋势是持续向体积更小、重量更轻的方向发展,其中芯片的封装体积,也基本体现了芯片的重量。以输入输出(I/O)脚数为24脚举例,将传统的DIP(Dual inline package)、SOP(Small outline package)和QFN做个粗略的对比(表-1):

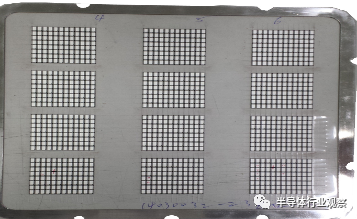

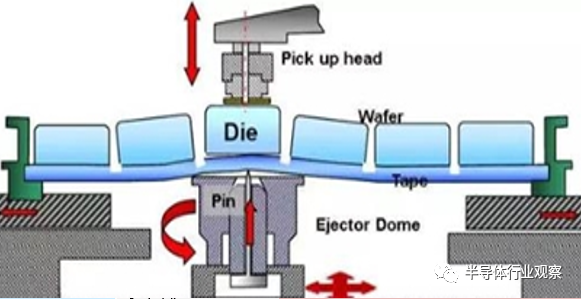

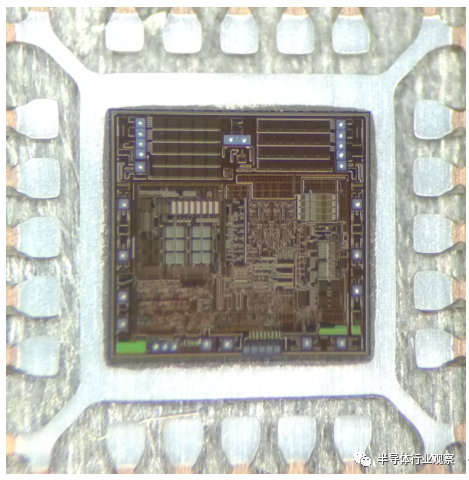

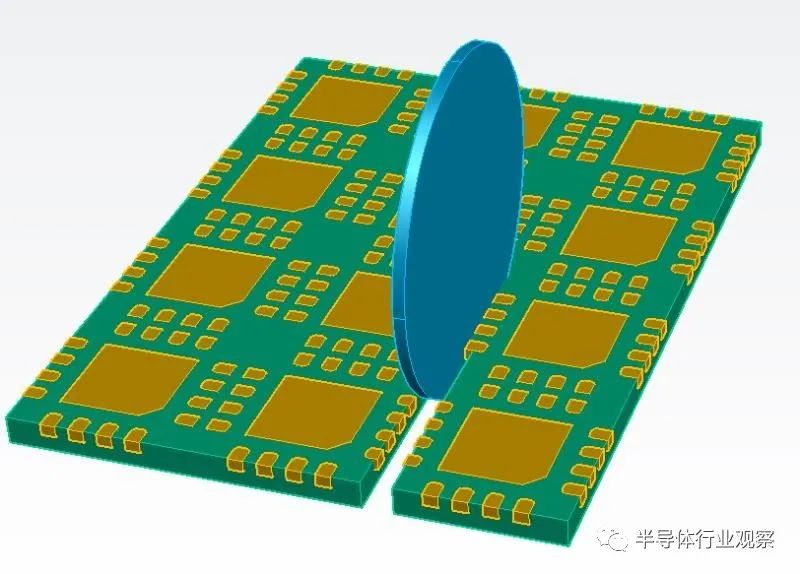

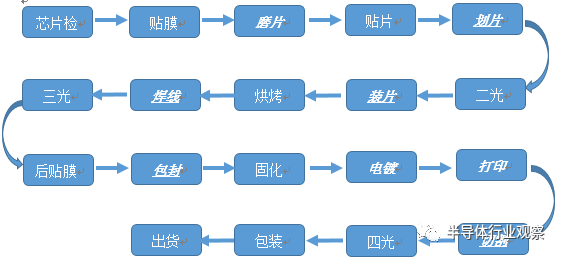

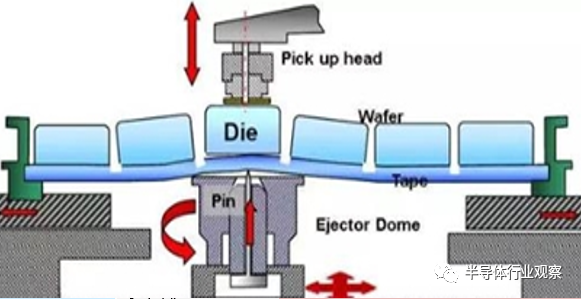

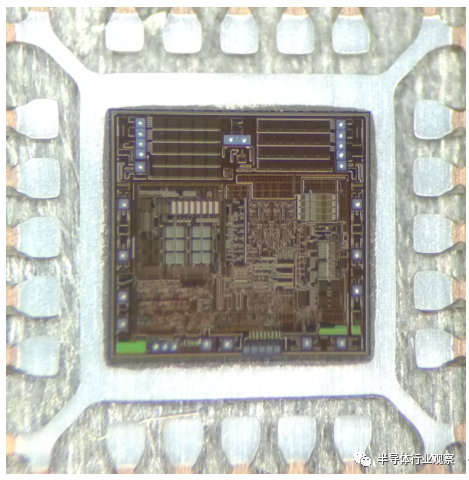

由表-1看出在传统封装里面,不论是芯片封装面积还是最终的芯片重量QFN封装都具有很大的竞争优势。实际上从封装效率(芯片面积与封装面积之比值趋向1为高效率)看,传统的DIP封装效率只有0.05~0.1非常低,SOP封装效率为0.1~0.2,而QFN封装效率可以做到0.3~0.4,无散热焊盘的QFN甚至可以做到0.5,间接说明QFN封装在传统封装类型中具有最高的封装效率。因此在空间受限、重量受限的条件下,QFN封装是个非常不错的选项。如图-1所示,QFN封装的底部中央位置通常有一个大面积裸露焊盘用来导热,这个焊盘可做直接散热通道,用于传导封装体内芯片工作产生的热量;焊盘经过表面贴装后直接焊接在电路板(PCB: printed circuit board)上,PCB散热孔可以把多余的功耗扩散到铜接地板中吸收多余的热量,极大提升了芯片的散热性。QFN封装不同于具有欧翼状引脚的传统DIP或SOP封装,QFN封装经过表面贴装后管脚与PCB焊盘之间的导电路径短,自感系数和封装体内的布线电阻很低,所以它也可以提供良好的电性能。QFN封装使用的载体多为平面设计金属框架,采用精准可控的蚀刻方式生产制造,因此具有框架表面处理方式多样化、结构设计多样化的特点,且搭配属性相吻合的塑封材料,可以改进、增强封装体内部各界层的结合力,阻止外部湿气进入产品内部造成芯片失效,增强产品可靠性;且QFN封装本身采用的就是金属载体不存在类似基板封装有吸收水汽的风险,因此QFN封装较传统的DIP、SOP甚至BGA、LGA(Land grid array)封装都可以具有更好的可靠性表现。如果单纯比较价格,QFN比不过传统的DIP/SOP封装;但是如果看性价比,QFN可能是目前所有封装中性价比最高的一种。在低阶性能芯片的红海市场,由于成本压力过大设计公司还会选择传统的DIP、SOP封装;但是在中等性能芯片的市场上,设计公司则往往会选择可造性强、成本合适的QFN封装,更高阶性能的芯片维持BGA或CSP封装。从实际案例来看,大型芯片设计公司在市场推广的时候往往会QFN和BGA两套封装方案同时推出(在芯片可使用QFN和BGA两种封装条件下),而QFN价格比BGA至少低30%,更好的配合公司销售策略;即使面对QFP(Qual flat package)封装,QFN也可以取得近15%的价格优势。QFN封装目前覆盖的芯片制造工艺范围非常广, 28nm工艺制造的芯片也有成功的大规模量产经验,加之上述三个方面的优点,整个市场对QFN在中端、中高端芯片更广泛应用抱有很大的信心。不论与传统DIP、SOP封装,或者与BGA、LGA、CSP(Chip level package)封装相比,QFN封装的流程都并不算复杂。QFN封装过程中主要站别有8个,其中4个可称为关键站别。主要站别有:磨片、划片、装片、焊线、包封、电镀、打印和切割,关键站别有装片、焊线、包封和切割。QFN封装简易流程图(图-5)如下:在封装厂内部,三光以及之前的站别称为前道工序,英文全称Front Of Line,简称FOL;把三光之后的站别称为后道工序,英文全称End Of Line,简称EOL。前道工序作业过程中,因为芯片裸露在作业环境中,环境的无尘等级卡控更为严苛,一般为1千级、1万级(每立方英尺中可含有直径大于0.5um的颗粒数不多于1千、1万),工作人员需穿连体防静电服工作;后道工序中的芯片经过塑封,有了物理保护所以无尘等级卡控较低为10万级(每立方英尺中含有直径大于0.5um颗粒数不多于10万个),工作人员穿普通防静电服即可。下面对8个主要站别的工作目的、常用设备进行简要描述说明,希望大家可以进一步了解QFN封装工艺的具体内容:磨片:对晶圆厂出来的圆片进行减薄的一道工序,方便在有限的空间中进行封装。从晶圆厂出来的圆片一般厚度为550~725um,而常规QFN封装总厚度也为550~750um,可见圆片如果不经过减薄处理,芯片将无法进行封装;目前主流的磨片设备来自日本的DISCO。划片:对圆片进行切割分离的一道工序,将一片圆片上成千上万个独立功能的芯片进行切割分离,方便后面封装。芯片的制造工艺、划片槽的结构设计、划片槽内的材料属性决定划片方式的选择(普通刀切、特殊镭射)。主流划片设备有来自日本的DISCO和精工。装片(图-6):将分离好的芯片从已划开的圆片上取出并放到金属载体(框架,图-7)上,芯片与金属载体通过银浆或粘结膜进行连接;装片的主流设备有来自新加坡的ASM和瑞士的ESEC。 图6

图6

图7

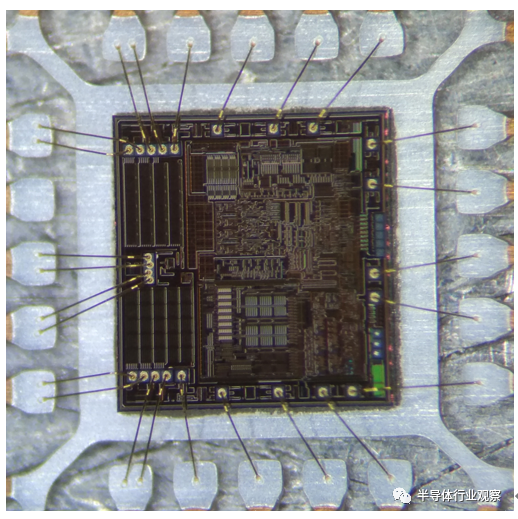

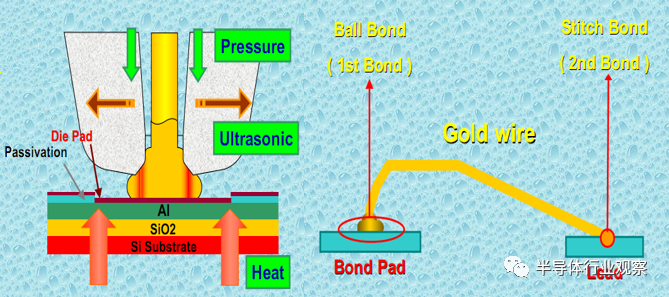

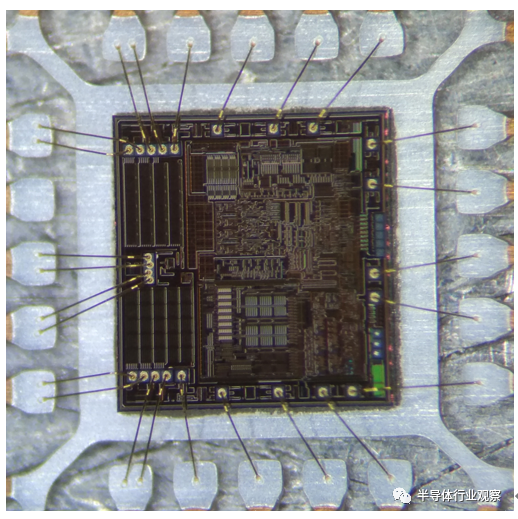

焊线(图-8):使用自动焊线设备将芯片的功能Pad与框架的管脚用焊线(金、银或铜线,图-9)连起来,把芯片设计的功能通过框架管脚连接到外面电路板确保产品通电后可以正常工作。焊线的主流设备来自美国设备产商K&S和新加坡ASM。

图9

图9

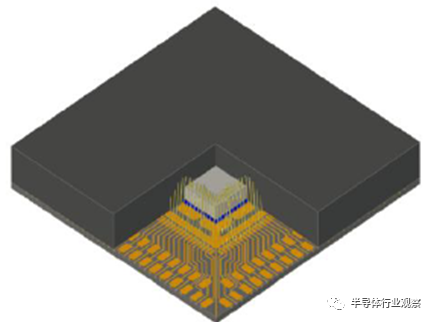

包封(图-10):使用自动注塑设备将已焊线好的芯片和金属载体用环氧树脂(通常黑色)通过高温压力注塑的方式覆盖包裹并且固化(图-11),在芯片外部形成物理保护。常用的设备来自日本的TOWA/YAMADA和新加坡的ASM。 图10

图10

图11

图11

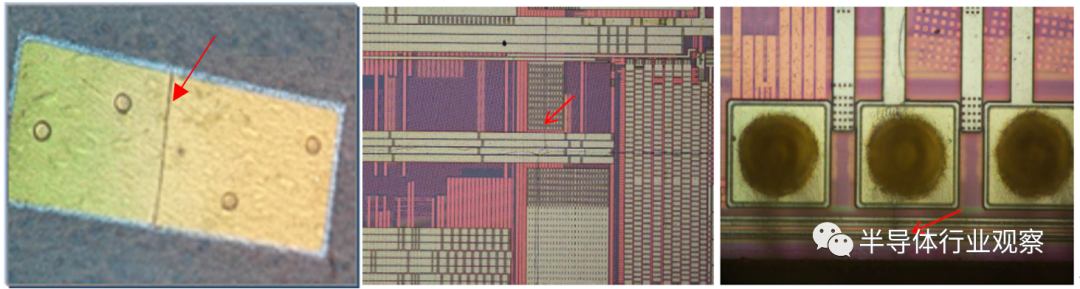

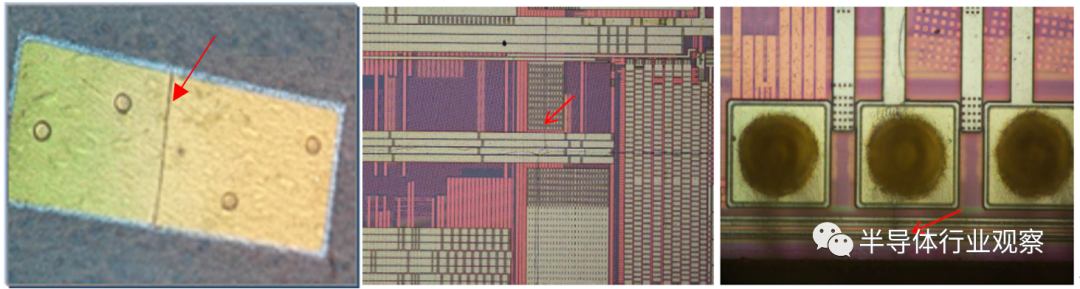

电镀:如果金属载体即框架背面为铜材,为了防止裸铜氧化并确保封装好的芯片可以用SMT(Surface mount technology)方式与电路板成功焊接,需要在铜材上镀上一层锡。设备可以选用国内的新阳、新基,这些设备供应商提供的设备已有成熟生产经验。打印:为了方便对芯片进行追溯,一般会使用激光打印设备在黑色环氧树脂表面将产品名称、客户标识甚至批次信息等打印在单颗产品上。常用的设备有来自台湾的钛昇、国内的新基。切割(图-12):前面工序作业过程中一定数量的芯片通常放置在条状框架载体上,最后需要将芯片用机械切割的方式分割开来(图-13)。常用的设备有来自日本的DISCO和韩国的HANMI。 图12上面介绍的QFN流程只是一个参考流程,依据各个工厂实际条件、产品作业状况、产品设计特点等,流程可能会有稍微不同,但整体原理保持一致。与所有其他封装形式一样,QFN封装在制造过程中也会产生很多缺陷,比如超薄QFN的芯片裂缝(图-14)、大颗QFN的碰线(图-15)和QFN特有的切割毛刺(图-16)等。发现缺陷并不可怕,需要考虑的是缺陷严重性、发生频率、侦测度,能否找到缺陷发生的真实原因和有无切实有效的改善方案。芯片裂缝(Die Crack)通常出现在超薄结构封装 (比如芯片厚度小于100um)、超大长宽比芯片(比如芯片长宽比大于6)和特殊材质芯片上(比如砷化镓芯片)。芯片裂缝因为不会影响后续工序作业,所以容易芯片封装全部完成后流到测试;如果测试程序不够精准,这种缺陷具有一定逃逸的风险并在终端造成质量事故。

图12上面介绍的QFN流程只是一个参考流程,依据各个工厂实际条件、产品作业状况、产品设计特点等,流程可能会有稍微不同,但整体原理保持一致。与所有其他封装形式一样,QFN封装在制造过程中也会产生很多缺陷,比如超薄QFN的芯片裂缝(图-14)、大颗QFN的碰线(图-15)和QFN特有的切割毛刺(图-16)等。发现缺陷并不可怕,需要考虑的是缺陷严重性、发生频率、侦测度,能否找到缺陷发生的真实原因和有无切实有效的改善方案。芯片裂缝(Die Crack)通常出现在超薄结构封装 (比如芯片厚度小于100um)、超大长宽比芯片(比如芯片长宽比大于6)和特殊材质芯片上(比如砷化镓芯片)。芯片裂缝因为不会影响后续工序作业,所以容易芯片封装全部完成后流到测试;如果测试程序不够精准,这种缺陷具有一定逃逸的风险并在终端造成质量事故。

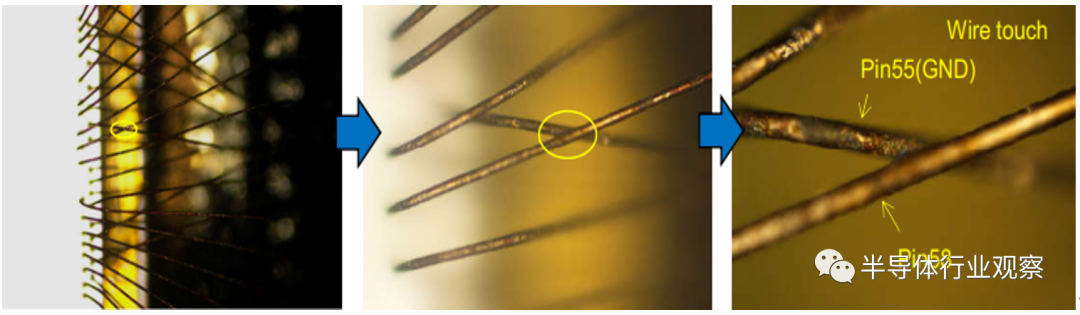

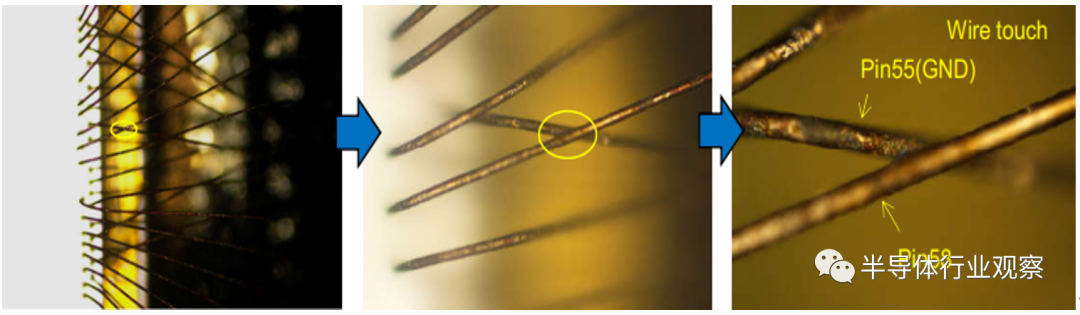

芯片裂缝发生后首先被怀疑的往往是装片站,因为装片的工作原理是“下顶上吸”(图-6),即芯片蓝膜下方用顶针往上顶、芯片正上方用吸嘴往上吸,使得最终芯片脱离蓝膜被放置到金属载体上。这作业过程当中,如果芯片厚度偏薄,顶针上顶作用力过于集中就容易导致芯片产生裂缝;另外如果芯片长宽比过大,装片一般会使用多顶针作业方式,此时倘若多顶针不在同一平面、作用力不同步也会导致芯片裂缝。有趣的是在实际工作中,我们往往发现从晶圆厂过来的已划砷化镓芯片会一定比例的芯片裂缝缺陷。所以最佳的芯片裂缝检查时机是划片之后、装片之前,可以由工人翻膜取下芯片在显微镜下确认;球焊之后的三光也可以检查芯片裂缝,只是因为已焊线在显微镜下有干扰且只能看正面(有些芯片裂缝并没有裂到芯片正面),检查不方便而容易逃逸;成品之后使用SAT方式也可以检测芯片分层,但操作难度、成本更高。因此,应了质量管理理念中的一条:不让缺陷流入下一站,是最佳的制造模式。大颗的QFN已渐成替代普通BGA封装的趋势,意味着QFN将引来更密集的焊线、更多脚位数的需求。焊线越密集,碰线(Wire Short)导致电性测试短路的风险越高,因此碰线是大颗QFN一个重大缺陷,特别是线弧尚未优化完成的初期量产阶段。碰线可以在低倍显微镜看出,通常情况下也可以在测试端筛选出来,因此逃逸的可能性较低。

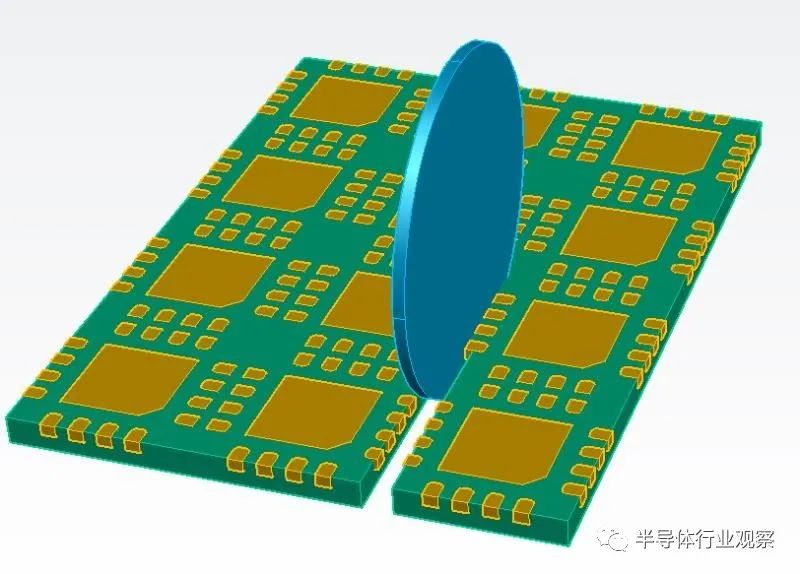

解决碰线的重点是焊线站,偶尔也需要包封站作出参数调整。焊线程序设置的好坏基本决定了碰线几率的大小,在近百种线弧模式、无数组线弧参数搭配中,寻找出最适合的线弧模式、最好的线弧参数组合,需要焊线工程师的丰富经验。优秀的焊线工程师不仅仅会在每层线弧之间会留有至少两倍线径空间,在空旷处但容易碰线的位置设置打弯模式,对长线弧选用合适的线弧模式,他还需要统筹考虑包封模流的方向、结合芯片位置、甚至封装结构提出改善方案,降低碰线几率。如果碰线发生集中在框架载体的末排、单颗芯片的回包区,包封工程师一般会对包封参数进行优化,比如分段设置注塑压力、优化分段位置;在包封参数无解的情况下包封工程师和焊线工程师往往会一起合作,讨论出最终的解决方案。切割毛刺(Bur,图-16),是QFN封装在切割工序中产生的一种缺陷,这种缺陷不可避免,通常规格是长度不大于0.05mm,且不得管脚与管脚相连。切割站是将框架整体切透并分离出单颗产品的一道工序。作业过程中切割刀需要把单颗产品之间的金属连接处切断,由于金属具有一定的延展性,在分离过程中必然会产生切割毛刺。切割毛刺在外观检验可以人工检查出来,也可以用光学检验设备自动检验,但由于目前检验设备的灵敏度不高,尚不能完全筛选出毛刺缺陷,因此毛刺具有一定的逃脱风险。对毛刺的解决重点大概可以从三个方向进行改进:1)优化框架设计:管脚跟部做收窄设计,正面采用半蚀刻工艺,管脚不到边设计;2)选用合适尺寸切割刀片、采用树脂刀片;3)优化切割参数,尤其是进刀速度。现在国内芯片设计公司在解决芯片“有与无”问题的同时,对封装出来的产品品质要求也逐渐向国际头部设计公司靠拢,因此在产品进入量产前,一整套的可靠性考核项目和报告不可或缺。一般来说,QFN常用的考核项目有预处理(Pre-con),高温存储试验(HTSL:high temperature storage life),温度循环试验(TCT: temperature cycle test),高压蒸煮试验(PCT: pressure cycle test),加速温湿度试验(UHAST: Ubias high accelerated stress test)和易焊性试验(ST: Solderbility test)。具体封装形式、对应的可靠性条件、要求,可以参考联合电子设备工程委员会(JEDEC: joint electron device engineering council)相关文件。目前采用QFN封装形式的芯片应用非常广泛:蓝牙芯片、音频芯片、电源管理芯片、功率放大芯片、基站时钟芯片、视频监控芯片等;另外由传统QFN衍生出来aQFN(Advanced QFN),DR-QFN(Dual row-QFN)、MIS(Molded-integrated System)因为可设计更多管脚并具有一定二次布线功能,也具有一定的开发潜力。QFN封装是一种极具适用能力强、结构简单、高性价比的封装形式,在可预见的5年内出现替代封装的可能性不高。QFN封装的开发方向目前明朗的有两个:大尺寸、模组化。QFN大尺寸化,契合的是电子终端产品选用的芯片封装从之前较高成本BGA/QFP封装的低成本化;目前封装尺寸12mm*12mm、内含400根以上焊线、多层芯片叠装的QFN产品已经进入大规模量产;更大尺寸的QFN封装也在厂内紧锣密鼓的安排验证,预计2021年Q4完成考核。QFN模组化,顺应的是电子产品小型化、多功能化、高集成度方向,只要这个方向不变QFN模组化的趋势就一直会存在。当前的QFN模组封装里面含有芯片、电容、电阻和电感,甚至包封好的芯片,基本可以看做一个微集成系统;在这个微小的系统里扎实耕耘,可能会别有洞天。

总之,随着芯片内部的摩尔定律走到尽头,我们有理由相信表现在芯片外部的封装工艺研究在芯片产业链中的重要性将会进一步得到体现;更为先进的封装技术、更为高效的封装方案,必定会助推芯片行业更进一步发展。

转自https://www.zzstt.cn/1?article_id=474

启闳半导体科技(江苏)有限公司

启闳半导体科技(江苏)有限公司

图4

图4

图6

图6

图9

图9

图10

图10 图11

图11

图12

图12