启闳半导体科技(江苏)有限公司

启闳半导体科技(江苏)有限公司设计流程( Design Flow)是指集成电路的设计过程中的优化、仿真、验证以及对应的数据输入/输出。从20世纪70年代起,为了应对日益增长的设计复杂度,根据设计对象不同,逐渐将设计流程分为若干阶段。集成电路的设计流程通常分为数字集成电路设计流程和模拟集成电路设计流程。

1.数字集成电路设计流程

数字集成电路设计流程(见图5-3)主要包括芯片定义(Specification)、 逻辑设计(Logic Design)、逻辑综合(Logic Synthesis)、物理设计(Physical Design)、物理验证( Physical Verification) 和版图交付(Tape Out,又称流片)等阶段。其中,物理设计又包括数据导入(Data Import)、布局规划( Floorplan)、单元布局(Placement)、时钟树综合(Clock Tree Synthesis)和布线(Routing)。 该设计流程是一个反复迭代(Iterations) 的过程。例如,在物理设计过程中,如果发现电路逻辑难以满足芯片定义的功能或者性能,必须返回逻辑设计重新设计;在布线过程中,如果发现布线资源紧缺,芯片布局规划不合理,必须返回布局规划重新规划:但在数字集成电路设计过程中,应尽可能避免大的迭代。

芯片定义是指根据市场或者用户需求制定芯片实现的功能和性能指标参数,完成设计规格文档。

逻辑设计是指根据架构设计,基于硬件描述语言,在寄存器传输级(Register-Transfer Level, RTL) 实现逻辑设计,并通过逻辑仿真验证或者形式验证等手段验证逻辑设计功能的正确性。

逻辑综合是指将RTL设计转换成特定目标(以约束描述)的门级网表,并优化门级网表的延时、面积和功耗等。

物理设计是指将门级网表根据时序等约束布局、布线并最终生成版图的过程,可以分为数据导入、布局规划、单元布局、时钟树综合和布线等步骤。数据导入是指导入综合后的网表(Netlist) 和具有时序约束的脚本文件,以及代工厂提供的库文件。布局规划是指在芯片上规定输入/输出单元、宏单元及其他主要模块位置的过程。单元布局是指根据网表和时序约束自动放置标准单元的过程。时钟树综合是指插入时钟缓冲器,生成时钟网络,最小化时钟延迟和时钟偏差的过程。布线是指在满足布线层数限制、线宽、线间距等约束条件下,根据电路关系自动连接各个单元的过程。

物理验证通常包括版图设计规则检查( Design Rule Check, DRC)、版图电路图一致性检查(Layout Versus Schematic, LVS)和电气规则检查( Elecronic Rule Check, ERC)等。

版图交付是在所有检查和验证都正确无误的前提下,传递版图文件给代工厂生成掩模图形,并生产芯片。

2.模拟集成电路设计流程

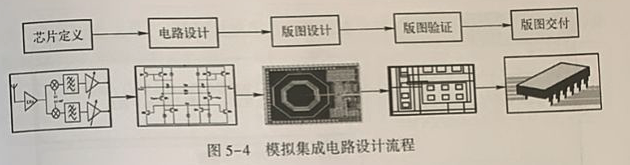

模拟集成电路设计流程主要有芯片定义( Specification)、电路设计(Circuit Design)、版图设计(Layout Design)、版图验证(Layout Verification) 和版图交付(Tape Out)等阶段,如图5-4所示。

电路设计是指根据系统需求,设计以晶体管级网表描述的模拟电路结构,并采用SPICE等仿真工具验证功能和性能。版图设计是指按照设计规则,以层次化的方式绘制其对应的版图几何图形,并通过版图验证验证版图的工艺规则、电气规则等,验证通过后再仿真验证电路功能和性能。

版图验证是指对芯片版图中的各层图形所进行的设计规则检查、电气规则检查和版图电路图致性检查等。

模拟集成电路设计的版图交付与数字集成电路设计的一样。

随着集成度的不断提高,设计成本和设计周期已成为集成电路产品研制成本和产品周期的主要部分,EDA 工具成为提高设计效率的关键。数字集成电路设计流程呈现出系统级设计、面向可制造性的设计、面向成品率的设计等发展趋势。适用于模拟集成电路的EDA工具也呈现出抽象层次越来越高的趋势,同时通过在现有工具架构上应用深度学习来优化设计的方法在EDA领域中呈现出新优势。